TESTING SERVICES

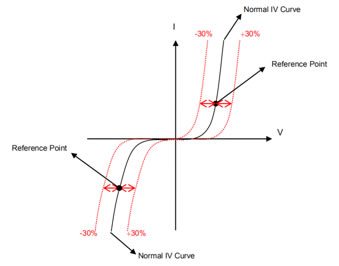

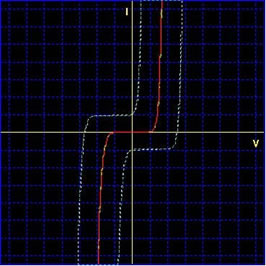

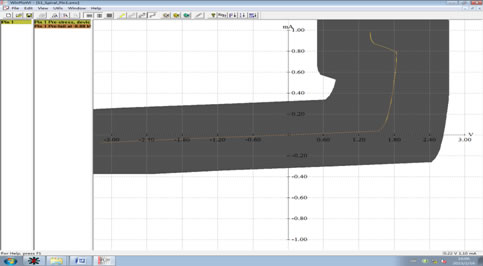

ESD & LATCH-UP TEST

The ESD testing can verify whether the anti-static ability of devices conforms to relevant standards, mainly including three modes: human body mode (HBM), machine mode (MM), and chip discharge mode (CDM).

The latch-up is caused by the parasitic transistor interaction between the power wire and ground wire in the CMOS manufacturing process, resulting in a low impedance path and causing high current between the power wire and ground wire, damaging the chip. According to the electrical parameters in the original manufacturer’s specifications, build a DUT board to connect to the testing machine, and then apply voltage or current to the device according to relevant standards to test whether the device will be damaged due to latch-up.

Application

Integrated Circuits, Transistors, Resistors, Capacitors, Inductors, Transformers, Sensors, Electromechanical Components, Connectors, PCB, PCBA, Power Modules, Signal Modules, etc

Reference Standards

JESD-78; JESD22-A115; JESD22-A144; JS-001; JS-002; IEC61000-4-2; MIL-STD-883; etc